DRA78x处理器采用Via Channel™阵列(VCA)技术,球栅阵列(FCBGA)封装,提供367球,15×15毫米,0.65毫米球距(信号上可以使用0.8毫米间距规则) 。

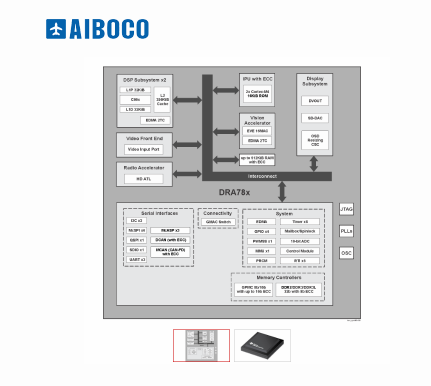

该体系结构旨在以经济高效的解决方案为协处理器,混合无线电和放大器应用提供高性能并发功能,从DRA75x(“ Jacinto 6 EP”和“ Jacinto 6 Ex”),“ DRA74x”提供全面的可扩展性。 Jacinto 6“,DRA72x” Jacinto 6 Eco“和DRA71x” Jacinto 6 Entry“系列信息娱乐处理器。

此外,德州仪器(TI)为Arm和DSP提供了一套完整的开发工具,包括C编译器和调试接口,以使您可以查看源代码的执行情况。

DRA78x Jacinto 6 RSP(无线电声音处理器)设备系列符合AEC-Q100标准。

该器件具有简化的电源轨映射,可实现低成本PMIC解决方案。

DRA78x处理器采用Via Channel™阵列(VCA)技术,球栅阵列(FCBGA)封装,提供367球,15×15毫米,0.65毫米球距(信号可使用0.8mm间距规则)。 。

该体系结构旨在以经济高效的解决方案为汽车协处理器,混合无线电和放大器应用提供高性能并发功能,从DRA75x(“ Jacinto 6 EP”和“ Jacinto 6 Ex”),“ DRA74x”提供全面的可扩展性。 Jacinto 6“,DRA72x” Jacinto 6 Eco“和DRA71x” Jacinto 6 Entry“系列信息娱乐处理器。

此外,德州仪器(TI)为Arm和DSP提供了一套完整的开发工具,包括C编译器和调试接口,以使您可以查看源代码的执行情况。

DRA78x Jacinto 6 RSP(无线电声音处理器)设备系列符合AEC-Q100标准。

该器件具有简化的电源轨映射,可实现低成本PMIC解决方案。

专为信息娱乐应用设计的架构

多达2个C66x浮点VLIW DSP

与C67x和C64x +完全兼容的目标代码

每个周期最多32个16×16位定点乘法

高达512kB的片上L3 RAM

3级(L3)和4级(L4)互连

内存接口(EMIF)模块

支持DDR3 / DDR3L至DDR-1066

支持DDR2至DDR-800

最高支持2GB

双臂®皮质® -M4(IPU)

视觉加速器

嵌入式视觉引擎(EVE)

显示子系统

带有DMA引擎的显示控制器

CVIDEO / SD-DAC电视模拟复合输出

片上温度传感器能够产生温度警报

通用内存控制器(GPMC)

增强型直接内存访问(EDMA)控制器

3端口(2个外部)千兆以太网(GMAC)交换机

控制器局域网(DCAN)模块

CAN 2.0B协议

模块化控制器局域网(MCAN)模块

CAN 2.0B协议

八个32位通用定时器

三个可配置的UART模块

四个多通道串行外围设备接口(McSPI)

四路SPI接口

两个内部集成电路(I 2 C™)端口

三个多通道音频串行端口(McASP)模块

安全数字输入输出接口(SDIO)

多达126个通用I / O(GPIO)引脚

电源,重置和时钟管理

使用CTools技术进行片上调试

符合汽车AEC-Q100标准

15×15毫米,0.65毫米间距,367引脚PBGA(ABF)

可以用作看门狗定时器的五个实时中断(RTI)模块实例

8通道10位ADC

脉宽调制

视频和图像处理支持

全高清视频(1920×1080p,60 fps)

视频输入和视频输出

GPIO不用于视频时

视频输入端口(VIP)模块

支持多达4个多路复用输入端口