# **ST-NXP Wireless**

# **IMPORTANT NOTICE**

Dear customer,

As from August 2<sup>nd</sup> 2008, the wireless operations of NXP have moved to a new company, ST-NXP Wireless.

As a result, the following changes are applicable to the attached document.

- Company name NXP B.V. is replaced with ST-NXP Wireless.

- **Copyright** the copyright notice at the bottom of each page "© NXP B.V. 200x. All rights reserved", shall now read: "© ST-NXP Wireless 200x All rights reserved".

- Web site <u>http://www.nxp.com</u> is replaced with <u>http://www.stnwireless.com</u>

- **Contact information** the list of sales offices previously obtained by sending an email to <u>salesaddresses@nxp.com</u>, is now found at <u>http://www.stnwireless.com</u> under Contacts.

If you have any questions related to the document, please contact our nearest sales office. Thank you for your cooperation and understanding.

ST-NXP Wireless

# ISP1562 Hi-Speed Universal Serial Bus PCI Host Controller Rev. 02 – 1 March 2007 Product data sheet

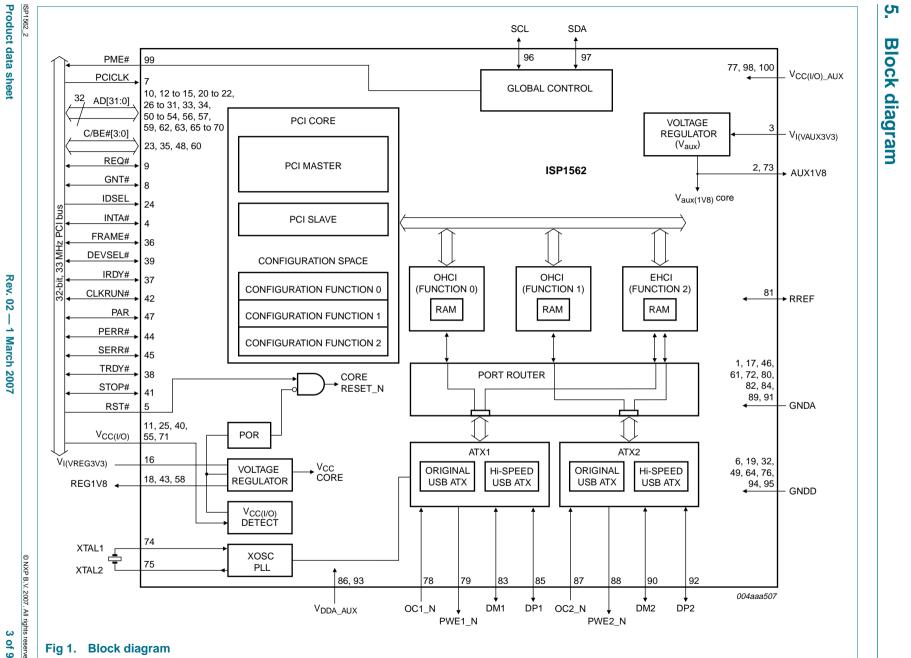

# 1. General description

The ISP1562 is a Peripheral Component Interconnect (PCI)-based, single-chip Universal Serial Bus (USB) Host Controller. It integrates two Original USB Open Host Controller Interface (OHCI) cores, one Hi-Speed USB Enhanced Host Controller Interface (EHCI) core, and two transceivers that are compliant with Hi-Speed USB and Original USB. The functional parts of the ISP1562 are fully compliant with *Universal Serial Bus Specification Rev. 2.0, Open Host Controller Interface Specification for USB Rev. 1.0a, Enhanced Host Controller Interface Specification for USB Rev. 1.0, PCI Local Bus Specification Rev. 2.2, and PCI Bus Power Management Interface Specification Rev. 1.1.*

Integrated high performance USB transceivers allow the ISP1562 to handle all Hi-Speed USB transfer speed modes: high-speed (480 Mbit/s), full-speed (12 Mbit/s) and low-speed (1.5 Mbit/s). The ISP1562 provides two downstream ports, allowing simultaneous connection of USB devices at different speeds.

The ISP1562 is fully compatible with various operating system drivers, such as Microsoft Windows standard OHCI and EHCI drivers that are present in Windows XP, Windows 2000 and Red Hat Linux.

The ISP1562 directly interfaces to any 32-bit, 33 MHz PCI bus. Its PCI pins can source 3.3 V. The PCI interface fully complies with *PCI Local Bus Specification Rev. 2.2*.

The ISP1562 is ideally suited for use in Hi-Speed USB mobile applications and embedded solutions. The ISP1562 uses a 12 MHz crystal.

# 2. Features

- Complies with Universal Serial Bus Specification Rev. 2.0

- Supports data transfer at high-speed (480 Mbit/s), full-speed (12 Mbit/s) and low-speed (1.5 Mbit/s)

- Two Original USB OHCI cores comply with Open Host Controller Interface Specification for USB Rev. 1.0a

- One Hi-Speed USB EHCI core complies with Enhanced Host Controller Interface Specification for Universal Serial Bus Rev. 1.0

- Supports PCI 32-bit, 33 MHz interface compliant with PCI Local Bus Specification Rev. 2.2, with support for D3<sub>cold</sub> standby and wake-up modes; all I/O pins are 3.3 V standard

- Compliant with PCI Bus Power Management Interface Specification Rev. 1.1 for all hosts (EHCI and OHCI), and supports all power states: D0, D1, D2, D3<sub>hot</sub> and D3<sub>cold</sub>

ISP1562

- CLKRUN support for mobile applications, such as internal notebook design

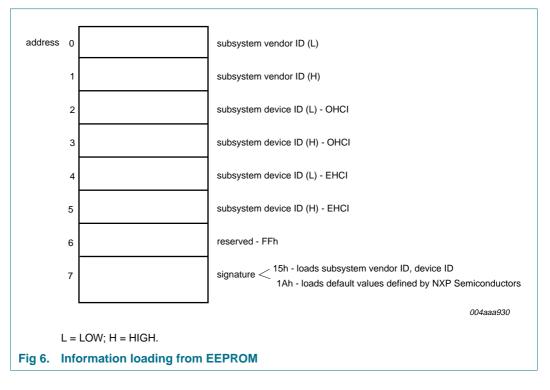

- Configurable subsystem ID and subsystem Vendor ID through external EEPROM

- Digital and analog power separation for better ElectroMagnetic Interference (EMI) and ElectroStatic Discharge (ESD) protection

- Supports hot Plug and Play and remote wake-up of peripherals

- Supports individual power switching and individual overcurrent protection for downstream ports

- Supports partial dynamic port-routing capability for downstream ports that allows sharing of the same physical downstream ports between the Original USB Host Controller and the Hi-Speed USB Host Controller

- Uses 12 MHz crystal oscillator to reduce system cost and EMI emissions

- Supports dual power supply: PCI V<sub>aux(3V3)</sub> and V<sub>CC</sub>

- Operates at +3.3 V power supply input

- Low power consumption

- Full industrial operating temperature range from -40 °C to +85 °C

- Full-scan design with high fault coverage (93 % to 95 %) ensures high quality

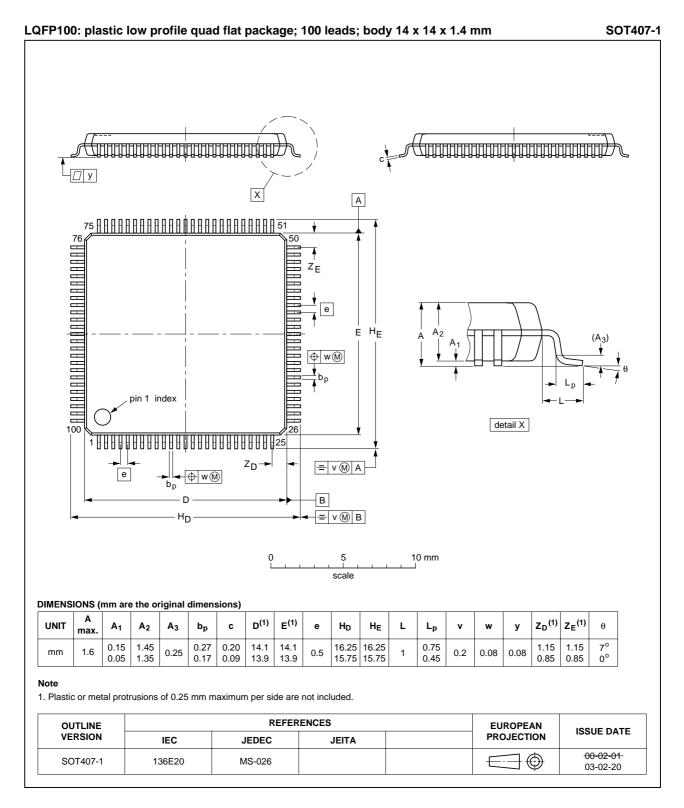

- Available in LQFP100 package

# 3. Applications

- Digital consumer appliances

- Notebook

- PCI add-on card

- PC motherboard

- Set-Top Box (STB)

- Web appliances

# 4. Ordering information

#### Table 1.Ordering information

| Type number | Package |                                                                                       |          |  |  |  |

|-------------|---------|---------------------------------------------------------------------------------------|----------|--|--|--|

|             | Name    | Description                                                                           | Version  |  |  |  |

| ISP1562BE   | LQFP100 | plastic low profile quad flat package; 100 leads; body 14 $\times$ 14 $\times$ 1.4 mm | SOT407-1 |  |  |  |

NXP Semiconductors

**HS USB PCI Host Controller**

**SP1562**

Rev. 22 <u>~</u> March 2007

> ω of 93

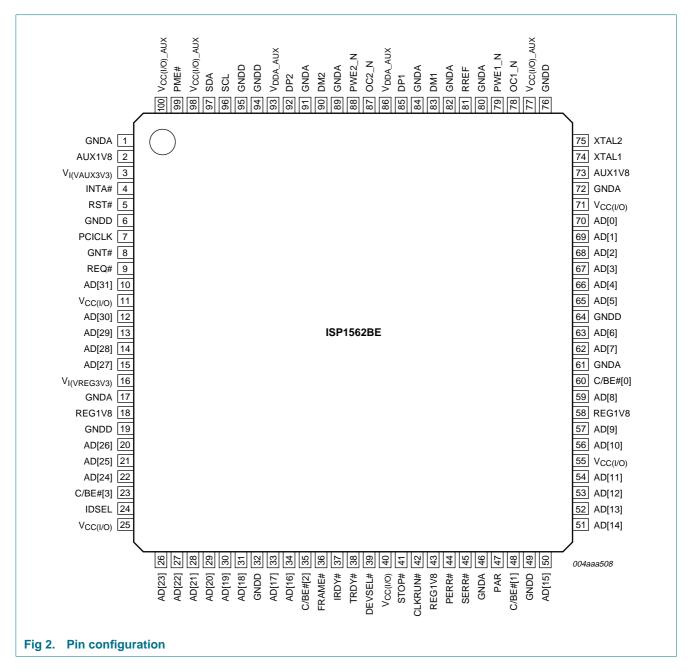

# 6. Pinning information

# 6.1 Pinning

# 6.2 Pin description

| Table 2.                | Pin des | cription |                                                                                                                                                                                                       |

|-------------------------|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol <sup>[1]</sup>   | Pin     | Туре     | Description                                                                                                                                                                                           |

| GNDA                    | 1       | -        | analog ground                                                                                                                                                                                         |

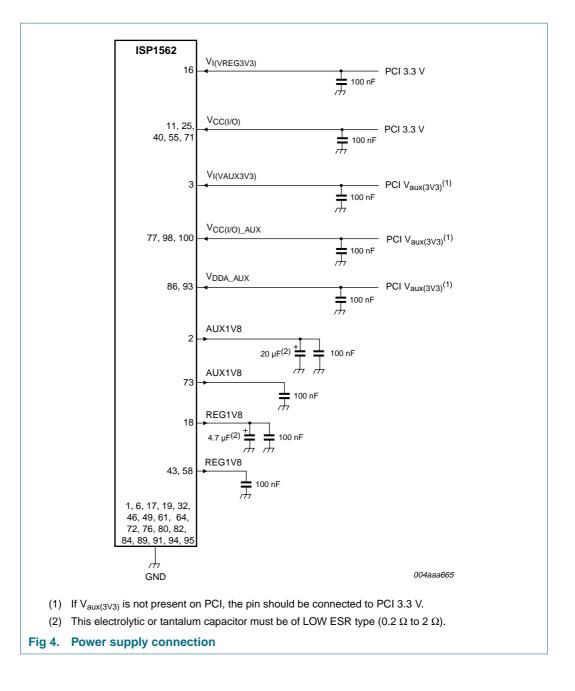

| AUX1V8                  | 2       | -        | 1.8 V auxiliary output voltage; only for voltage conditioning; cannot be used to supply power to external components; connected to 100 nF and 20 $\mu F$ capacitors                                   |

| V <sub>I(VAUX3V3)</sub> | 3       | -        | 3.3 V auxiliary input voltage; add a 100 nF decoupling capacitor                                                                                                                                      |

| INTA#                   | 4       | 0        | PCI interrupt<br>PCI pad; 3.3 V signaling; open-drain                                                                                                                                                 |

| RST#                    | 5       | I        | PCI reset; used to bring PCI-specific registers, sequencers and signals to a consistent state<br>3.3 V input pad; push-pull; CMOS                                                                     |

| GNDD                    | 6       | -        | digital ground                                                                                                                                                                                        |

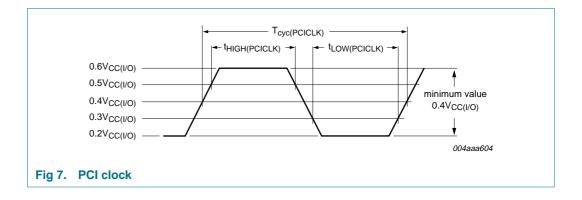

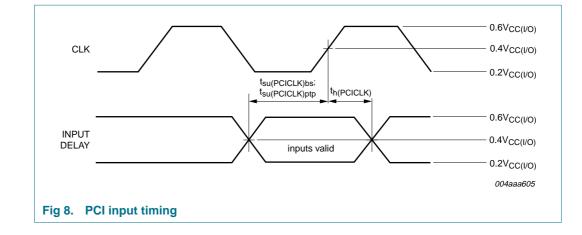

| PCICLK                  | 7       | I        | PCI system clock; see Table 118                                                                                                                                                                       |

|                         |         |          | PCI pad; 3.3 V signaling                                                                                                                                                                              |

| GNT#                    | 8       | I/O      | PCI grant; indicates to the agent that access to the bus is granted                                                                                                                                   |

|                         | 0       | I/O      | PCI pad; 3.3 V signaling                                                                                                                                                                              |

| REQ#                    | 9       | 1/0      | PCI request; indicates to the arbitrator that the agent wants to use the bus<br>PCI pad; 3.3 V signaling                                                                                              |

| AD[31]                  | 10      | I/O      | bit 31 of multiplexed PCI address and data                                                                                                                                                            |

| / [0.]                  |         |          | PCI pad; 3.3 V signaling                                                                                                                                                                              |

| V <sub>CC(I/O)</sub>    | 11      | -        | 3.3 V supply voltage; used to power pads; add a 100 nF decoupling capacitor                                                                                                                           |

| AD[30]                  | 12      | I/O      | bit 30 of multiplexed PCI address and data<br>PCI pad; 3.3 V signaling                                                                                                                                |

| AD[29]                  | 13      | I/O      | bit 29 of multiplexed PCI address and data<br>PCI pad; 3.3 V signaling                                                                                                                                |

| AD[28]                  | 14      | I/O      | bit 28 of multiplexed PCI address and data                                                                                                                                                            |

| AD[20]                  | 14      | 1/0      | PCI pad; 3.3 V signaling                                                                                                                                                                              |

| AD[27]                  | 15      | I/O      | bit 27 of multiplexed PCI address and data                                                                                                                                                            |

|                         |         |          | PCI pad; 3.3 V signaling                                                                                                                                                                              |

| V <sub>I(VREG3V3)</sub> | 16      | -        | 3.3 V regulator input voltage; add a 100 nF decoupling capacitor                                                                                                                                      |

| GNDA                    | 17      | -        | analog ground                                                                                                                                                                                         |

| REG1V8                  | 18      | -        | 1.8 V regulator output voltage; only for voltage conditioning; cannot<br>be used to supply power to external components; connected to a<br>100 nF capacitor and a 4.7 $\mu$ F-to-10 $\mu$ F capacitor |

| GNDD                    | 19      | -        | digital ground                                                                                                                                                                                        |

| AD[26]                  | 20      | I/O      | bit 26 of multiplexed PCI address and data<br>PCI pad; 3.3 V signaling                                                                                                                                |

| AD[25]                  | 21      | I/O      | bit 25 of multiplexed PCI address and data                                                                                                                                                            |

| ·- [-•]                 |         |          | PCI pad; 3.3 V signaling                                                                                                                                                                              |

| AD[24]                  | 22      | I/O      | bit 24 of multiplexed PCI address and data<br>PCI pad; 3.3 V signaling                                                                                                                                |

ISP1562\_2 Product data sheet

| Table 2. F           | Pin des<br>Pin | Type | Description                                                                                                                       |

|----------------------|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------|

| C/BE#[3]             | 23             | I/O  | byte 3 of multiplexed PCI bus command and byte enable                                                                             |

| 0/DL#[3]             | 20             | 1/0  | PCI pad; 3.3 V signaling                                                                                                          |

| IDSEL                | 24             | I    | PCI initialization device select; used as a chip select during configuration read and write transactions PCI pad; 3.3 V signaling |

| V <sub>CC(I/O)</sub> | 25             | -    | <ul><li>3.3 V supply voltage; used to power pads; add a 100 nF decoupling capacitor</li></ul>                                     |

| AD[23]               | 26             | I/O  | bit 23 of multiplexed PCI address and data                                                                                        |

| [ -]                 | -              |      | PCI pad; 3.3 V signaling                                                                                                          |

| AD[22]               | 27             | I/O  | bit 22 of multiplexed PCI address and data<br>PCI pad; 3.3 V signaling                                                            |

| AD[21]               | 28             | I/O  | bit 21 of multiplexed PCI address and data<br>PCI pad; 3.3 V signaling                                                            |

| AD[20]               | 29             | I/O  | bit 20 of multiplexed PCI address and data<br>PCI pad; 3.3 V signaling                                                            |

| AD[19]               | 30             | I/O  | bit 19 of multiplexed PCI address and data<br>PCI pad; 3.3 V signaling                                                            |

| AD[18]               | 31             | I/O  | bit 18 of multiplexed PCI address and data<br>PCI pad; 3.3 V signaling                                                            |

| GNDD                 | 32             | -    | digital ground                                                                                                                    |

| AD[17]               | 33             | I/O  | bit 17 of multiplexed PCI address and data                                                                                        |

|                      |                |      | PCI pad; 3.3 V signaling                                                                                                          |

| AD[16]               | 34             | I/O  | bit 16 of multiplexed PCI address and data                                                                                        |

|                      |                |      | PCI pad; 3.3 V signaling                                                                                                          |

| C/BE#[2]             | 35             | I/O  | byte 2 of multiplexed PCI bus command and byte enable                                                                             |

|                      |                |      | PCI pad; 3.3 V signaling                                                                                                          |

| FRAME#               | 36             | I/O  | PCI cycle frame; driven by the master to indicate the beginning and duration of an access                                         |

|                      |                |      | PCI pad; 3.3 V signaling                                                                                                          |

| IRDY#                | 37             | I/O  | PCI initiator ready; indicates the ability of the initiating agent to complete the current data phase of a transaction            |

|                      |                |      | PCI pad; 3.3 V signaling                                                                                                          |

| TRDY#                | 38             | I/O  | PCI target ready; indicates the ability of the target agent to complete the current data phase of a transaction                   |

|                      | 20             | 1/0  | PCI pad; 3.3 V signaling                                                                                                          |

| DEVSEL#              | 39             | I/O  | PCI device select; indicates if any device is selected on the bus<br>PCI pad; 3.3 V signaling                                     |

| V <sub>CC(I/O)</sub> | 40             | -    | 3.3 V supply voltage; used to power pads; add a 100 nF decoupling capacitor                                                       |

| STOP#                | 41             | I/O  | PCI stop; indicates that the current target is requesting the master to stop the current transaction                              |

|                      |                |      | PCI pad; 3.3 V signaling                                                                                                          |

| CLKRUN#              | 42             | I/O  | PCI CLKRUN signal; pull-down to ground through a 10 k $\Omega$ resistor PCI pad; 3.3 V signaling; open-drain                      |

|                       |     | -    | continued                                                                                                                                                                                                                    |

|-----------------------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol <sup>[1]</sup> | Pin | Туре | Description                                                                                                                                                                                                                  |

| REG1V8                | 43  | -    | 1.8 V regulator output voltage; only for voltage conditioning; cannot<br>be used to supply power to external components; add a 100 nF<br>decoupling capacitor                                                                |

| PERR#                 | 44  | I/O  | PCI parity error; used to report data parity errors during all PCI transactions, except a special cycle PCI pad; 3.3 V signaling                                                                                             |

| SERR#                 | 45  | 0    | PCI system error; used to report address parity errors and data parity<br>errors on the Special Cycle command, or any other system error in<br>which the result will be catastrophic<br>PCI pad; 3.3 V signaling; open-drain |

| GNDA                  | 46  | -    | analog ground                                                                                                                                                                                                                |

| PAR                   | 47  | I/O  | PCI parity                                                                                                                                                                                                                   |

|                       |     | ., • | PCI pad; 3.3 V signaling                                                                                                                                                                                                     |

| C/BE#[1]              | 48  | I/O  | byte 1 of multiplexed PCI bus command and byte enable<br>PCI pad; 3.3 V signaling                                                                                                                                            |

| GNDD                  | 49  | -    | digital ground                                                                                                                                                                                                               |

| AD[15]                | 50  | I/O  | bit 15 of multiplexed PCI address and data<br>PCI pad; 3.3 V signaling                                                                                                                                                       |

| AD[14]                | 51  | I/O  | bit 14 of multiplexed PCI address and data<br>PCI pad; 3.3 V signaling                                                                                                                                                       |

| AD[13]                | 52  | I/O  | bit 13 of multiplexed PCI address and data<br>PCI pad; 3.3 V signaling                                                                                                                                                       |

| AD[12]                | 53  | I/O  | bit 12 of multiplexed PCI address and data<br>PCI pad; 3.3 V signaling                                                                                                                                                       |

| AD[11]                | 54  | I/O  | bit 11 of multiplexed PCI address and data<br>PCI pad; 3.3 V signaling                                                                                                                                                       |

| V <sub>CC(I/O)</sub>  | 55  | -    | $3.3\ V$ supply voltage; used to power pads; add a 100 nF decoupling capacitor                                                                                                                                               |

| AD[10]                | 56  | I/O  | bit 10 of multiplexed PCI address and data<br>PCI pad; 3.3 V signaling                                                                                                                                                       |

| AD[9]                 | 57  | I/O  | bit 9 of multiplexed PCI address and data<br>PCI pad; 3.3 V signaling                                                                                                                                                        |

| REG1V8                | 58  | -    | 1.8 V regulator output voltage; only for voltage conditioning; cannot be used to supply power to external components; add a 100 nF decoupling capacitor                                                                      |

| AD[8]                 | 59  | I/O  | bit 8 of multiplexed PCI address and data<br>PCI pad; 3.3 V signaling                                                                                                                                                        |

| C/BE#[0]              | 60  | I/O  | byte 0 of multiplexed PCI bus command and byte enable PCI pad; 3.3 V signaling                                                                                                                                               |

| GNDA                  | 61  | -    | analog ground                                                                                                                                                                                                                |

| AD[7]                 | 62  | I/O  | bit 7 of multiplexed PCI address and data<br>PCI pad; 3.3 V signaling                                                                                                                                                        |

| AD[6]                 | 63  | I/O  | bit 6 of multiplexed PCI address and data<br>PCI pad; 3.3 V signaling                                                                                                                                                        |

ISP1562\_2 Product data sheet

| Table 2. F               | Pin des | cription | continued                                                                                                                                               |

|--------------------------|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol <sup>[1]</sup>    | Pin     | Туре     | Description                                                                                                                                             |

| GNDD                     | 64      | -        | digital ground                                                                                                                                          |

| AD[5]                    | 65      | I/O      | bit 5 of multiplexed PCI address and data                                                                                                               |

|                          |         |          | PCI pad; 3.3 V signaling                                                                                                                                |

| AD[4]                    | 66      | I/O      | bit 4 of multiplexed PCI address and data                                                                                                               |

|                          |         |          | PCI pad; 3.3 V signaling                                                                                                                                |

| AD[3]                    | 67      | I/O      | bit 3 of multiplexed PCI address and data                                                                                                               |

|                          |         |          | PCI pad; 3.3 V signaling                                                                                                                                |

| AD[2]                    | 68      | I/O      | bit 2 of multiplexed PCI address and data                                                                                                               |

|                          |         |          | PCI pad; 3.3 V signaling                                                                                                                                |

| AD[1]                    | 69      | I/O      | bit 1 of multiplexed PCI address and data                                                                                                               |

|                          |         |          | PCI pad; 3.3 V signaling                                                                                                                                |

| AD[0]                    | 70      | I/O      | bit 0 of multiplexed PCI address and data                                                                                                               |

|                          |         |          | PCI pad; 3.3 V signaling                                                                                                                                |

| V <sub>CC(I/O)</sub>     | 71      | -        | 3.3 V supply voltage; used to power pads; add a 100 nF decoupling capacitor                                                                             |

| GNDA                     | 72      | -        | analog ground                                                                                                                                           |

| AUX1V8                   | 73      | -        | 1.8 V auxiliary output voltage; only for voltage conditioning; cannot be used to supply power to external components; add a 100 nF decoupling capacitor |

| XTAL1                    | 74      | AI       | crystal oscillator input; this can also be a 12 MHz clock input                                                                                         |

| XTAL2                    | 75      | AO       | crystal oscillator output (12 MHz); leave open when clock is used                                                                                       |

| GNDD                     | 76      | -        | digital ground                                                                                                                                          |

| V <sub>CC(I/O)_AUX</sub> | 77      | -        | 3.3 V auxiliary supply voltage; used to power pads; add a 100 nF decoupling capacitor                                                                   |

| OC1_N                    | 78      | I        | overcurrent sense input for the USB downstream port 1 (digital)                                                                                         |

|                          |         |          | 3.3 V input pad; push-pull; CMOS                                                                                                                        |

| PWE1_N                   | 79      | 0        | power enable for the USB downstream port 1                                                                                                              |

|                          |         |          | 3.3 V output pad; 3 ns slew rate control; CMOS; open-drain                                                                                              |

| GNDA                     | 80      | -        | analog ground                                                                                                                                           |

| RREF                     | 81      | AI/O     | analog connection for the external resistor (12 k $\Omega\pm$ 1 %)                                                                                      |

| GNDA                     | 82      | -        | analog ground                                                                                                                                           |

| DM1                      | 83      | AI/O     | D–; analog connection for the USB downstream port 1; pull-down to ground through a 15 $k\Omega$ resistor                                                |

| GNDA                     | 84      | -        | analog ground                                                                                                                                           |

| DP1                      | 85      | AI/O     | D+; analog connection for the USB downstream port 1; pull-down to ground through a 15 $k\Omega$ resistor                                                |

| V <sub>DDA_AUX</sub>     | 86      | -        | auxiliary analog supply voltage; add a 100 nF decoupling capacitor                                                                                      |

| OC2_N                    | 87      | I        | overcurrent sense input for the USB downstream port 2 (digital)                                                                                         |

|                          |         |          | 3.3 V input pad; push-pull; CMOS                                                                                                                        |

| PWE2_N                   | 88      | 0        | power enable for the USB downstream port 2                                                                                                              |

|                          |         |          | 3.3 V output pad; 3 ns slew rate control; CMOS; open-drain                                                                                              |

| GNDA                     | 89      | -        | analog ground                                                                                                                                           |

| Table 2.                 | Pin des | cription | continued                                                                                                                                 |

|--------------------------|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol <sup>[1]</sup>    | Pin     | Туре     | Description                                                                                                                               |

| DM2                      | 90      | AI/O     | D–; analog connection for the USB downstream port 2; pull-down to ground through a 15 $k\Omega$ resistor                                  |

| GNDA                     | 91      | -        | analog ground                                                                                                                             |

| DP2                      | 92      | AI/O     | D+; analog connection for the USB downstream port 2; pull-down to ground through a 15 $k\Omega$ resistor                                  |

| V <sub>DDA_AUX</sub>     | 93      | -        | auxiliary analog supply voltage; add a 100 nF decoupling capacitor                                                                        |

| GNDD                     | 94      | -        | digital ground                                                                                                                            |

| GNDD                     | 95      | -        | digital ground                                                                                                                            |

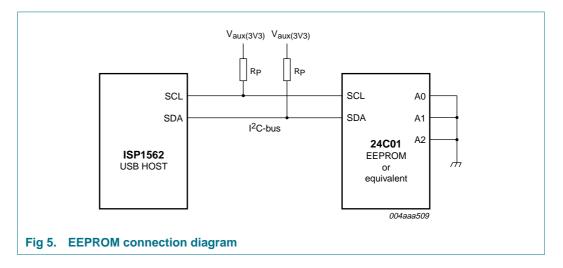

| SCL                      | 96      | I/O      | $I^2C$ -bus clock; pull-up to 3.3 V through a 10 k $\Omega$ resistor $^{[2]}$ $I^2C$ -bus pad; clock signal                               |

| SDA                      | 97      | I/O      | l <sup>2</sup> C-bus data; pull-up to 3.3 V through a 10 kΩ resistor <sup>[2]</sup> l <sup>2</sup> C-bus pad; data signal                 |

| V <sub>CC(I/O)_AUX</sub> | 98      | -        | 3.3 V auxiliary supply voltage; used to power pads; add a 100 nF decoupling capacitor                                                     |

| PME#                     | 99      | 0        | PCI Power Management Event; used by a device to request a change in the device or system power state PCI pad; 3.3 V signaling; open-drain |

| V <sub>CC(I/O)_AUX</sub> | 100     | -        | 3.3 V auxiliary supply voltage; used to power pads; add a 100 nF decoupling capacitor                                                     |

[1] Symbol names ending with # represent active LOW signals for PCI pins, for example: NAME#. Symbol names ending with underscore N represent active LOW signals for USB pins, for example: NAME\_N.

[2] Connect to ground if I<sup>2</sup>C-bus is not used.

# 7. Functional description

## 7.1 OHCI Host Controller

An OHCI Host Controller per port transfers data to devices at the Original USB defined bit rate of 12 Mbit/s or 1.5 Mbit/s.

# 7.2 EHCI Host Controller

The EHCI Host Controller transfers data to a Hi-Speed USB compliant device at the Hi-Speed USB defined bit rate of 480 Mbit/s. When the EHCI Host Controller has the ownership of a port, OHCI Host Controllers are not allowed to modify the port register. All additional port bit definitions required for the enhanced Host Controller are not visible to the OHCI Host Controller.

## 7.3 Dynamic port-routing logic

The port-routing feature allows sharing of the same physical downstream ports between the Original USB Host Controller and the Hi-Speed USB Host Controller. This requirement of *Enhanced Host Controller Interface Specification for Universal Serial Bus Rev. 1.0* provides ports that are multiplexed with the ports of the OHCI.

The EHCI is responsible for the port-routing switching mechanism. Two register bits are used for ownership switching. During power-on and system reset, the default ownership of all downstream ports is the OHCI. The enhanced Host Controller Driver (HCD) controls the ownership during normal functionality.

# 7.4 Hi-Speed USB analog transceivers

The Hi-Speed USB analog transceivers directly interface to the USB cables through integrated termination resistors. These transceivers can transmit and receive serial data at all data rates: high-speed (480 Mbit/s), full-speed (12 Mbit/s) and low-speed (1.5 Mbit/s).

## 7.5 Power management

The ISP1562 provides an advanced power management capability interface that is compliant with *PCI Bus Power Management Interface Specification Rev. 1.1*. Power is controlled and managed by the interaction between drivers and PCI registers.

For a detailed description on power management, see Section 10.

# 7.6 Phase-Locked Loop (PLL)

A 12 MHz-to-30 MHz and 48 MHz clock multiplier PLL is integrated on-chip. This allows the use of a low-cost 12 MHz crystal, which also minimizes EMI. No external components are required for the PLL to operate.

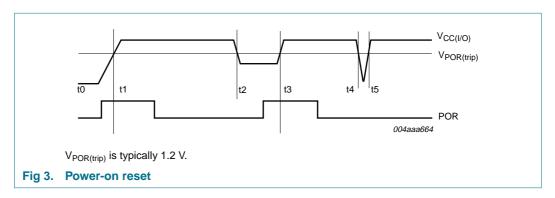

# 7.7 Power-On Reset (POR)

Figure 3 shows a possible curve of  $V_{CC(I/O)}$  with dips at t2 to t3 and t4 to t5. At t0, POR will start with 1. At t1, the detector passes through the trip level. Another delay will be added before POR drops to 0 to ensure that the length of the generated detector pulse, POR, is large enough to reset asynchronous flip-flops. If the dip is too short (t4 to t5 < 11  $\mu$ s), POR will not react and will stay LOW.

## 7.8 Power supply

Figure 4 shows the ISP1562 power supply connection.

**ISP1562**

**HS USB PCI Host Controller**

# 8.1 PCI interface

The PCI interface has three functions. The first function (#0) and the second function (#1) are for OHCI Host Controllers, and the third function (#2) is for the EHCI Host Controller. All functions support both master and target accesses, and share the same PCI interrupt signal INTA#. These functions provide memory-mapped, addressable operational registers as required in *Open Host Controller Interface Specification for USB Rev. 1.0a* and *Enhanced Host Controller Interface Specification for Universal Serial Bus Rev. 1.0.*

Each function has its own configuration space. The PCI enumerator must allocate the memory address space for each of these functions. Power management is implemented in each PCI function and all power states are provided. This allows the system to achieve low power consumption by switching off the functions that are not required.

#### 8.1.1 PCI configuration space

*PCI Local Bus Specification Rev. 2.2* requires that each of the three PCI functions of the ISP1562 provides its own PCI configuration registers, which can vary in size. In addition to the basic PCI configuration header registers, these functions implement capability registers to support power management.

The registers of each of these functions are accessed by the respective driver. <u>Section 8.2</u> provides a detailed description of various PCI configuration registers.

#### 8.1.2 PCI initiator and target

A PCI initiator initiates PCI transactions to the PCI bus. A PCI target responds to PCI transactions as a slave. In the ISP1562, two Open Host Controllers and the enhanced Host Controller function as both initiators or targets of PCI transactions issued by the host CPU.

All USB Host Controllers have their own operational registers that can be accessed by the system driver software. Drivers use these registers to configure the Host Controller hardware system, issue commands to it, and monitor the status of the current hardware operation. The Host Controller plays the role of a PCI target. All operational registers of the Host Controllers are the PCI transaction targets of the CPU.

Normal USB transfers require the Host Controller to access system memory fields, which are allocated by USB HCDs and PCI drivers. The Host Controller hardware interacts with the HCD by accessing these buffers. The Host Controller works as an initiator in this case and becomes a PCI master.

# 8.2 PCI configuration registers

OHCI USB Host Controllers and the EHCI USB Host Controller contain two sets of software-accessible hardware registers: PCI configuration registers and memory-mapped Host Controller registers.

A set of configuration registers is implemented for each of the three PCI functions of the ISP1562, see Table 3.

**Remark:** In addition to the normal PCI header, from offset index 00h to 3Fh, implementation-specific registers are defined to support power management and function-specific features.

| Address                            | Bits 31 to 24 Bits 23 to 16 |           | Bits 15 to 8 Bits 7 to 0 |            | Reset value <sup>[1]</sup> |                    |                    |  |

|------------------------------------|-----------------------------|-----------|--------------------------|------------|----------------------------|--------------------|--------------------|--|

|                                    |                             |           |                          |            | Func0 OHCI1                | Func1 OHCl2        | Func2 EHCI         |  |

| PCI configuration header registers |                             |           |                          |            |                            |                    |                    |  |

| 00h                                | DID[                        | DID[15:0] |                          | VID[15:0]  |                            | 1561 1131h         | 1562 1131h         |  |

| 04h                                | STATUS[15:0]                |           | CMD[15:0]                |            | 0210 <b>0000</b> h         | 0210 <b>0000</b> h | 0210 <b>0000</b> h |  |

| 08h                                |                             | CC[23:0]  |                          | REVID[7:0] | 0C03 1011h                 | 0C03 1011h         | 0C03 2011h         |  |

#### Table 3. PCI configuration space registers of OHCI1, OHCI2 and EHCI

| Address  | Bits 31 to 24    | Bits 23 to 16                       | Bits 15 to 8           | Bits 7 to 0      |                                     | Reset value <sup>[1]</sup>        |                                  |  |  |

|----------|------------------|-------------------------------------|------------------------|------------------|-------------------------------------|-----------------------------------|----------------------------------|--|--|

|          |                  |                                     |                        |                  | Func0 OHCI1                         | Func1 OHCI2                       | Func2 EHCI                       |  |  |

| 0Ch      | reserved HT[7:0] |                                     | LT[7:0] CLS[7:0]       |                  | 0080 <b>0000</b> h                  | 0080 <b>0000</b> h                | 0080 <b>0000</b> h               |  |  |

| 10h      |                  | BAR0                                | [31:0]                 |                  | <b>0000 0</b> 000h                  | <b>0000 0</b> 000h                | <b>0000 00</b> 00h               |  |  |

| 14h      |                  |                                     |                        |                  |                                     |                                   |                                  |  |  |

| 18h      |                  |                                     |                        |                  |                                     |                                   |                                  |  |  |

| 1Ch      |                  | rese                                | nucd                   |                  | 0000 0000h                          | 0000 0000h                        | 0000 0000h                       |  |  |

| 20h      |                  | Tese                                | Iveu                   |                  | 0000 000011                         | 0000 0000n                        | 0000 000011                      |  |  |

| 24h      |                  |                                     |                        |                  |                                     |                                   |                                  |  |  |

| 28h      |                  |                                     |                        |                  |                                     |                                   |                                  |  |  |

| 2Ch      | SID[             | 15:0]                               | SVID                   | [15:0]           | 1561 1131h                          | 1561 1131h                        | 1562 1131h                       |  |  |

| 30h      |                  | reserved 0000 0000h 0000 0000h 0000 |                        |                  | 0000 0000h                          |                                   |                                  |  |  |

| 34h      |                  | reserved                            |                        | CP[7:0]          | 0000 00DCh                          | 0000 00DCh                        | 0000 00DCh                       |  |  |

| 38h      |                  | rese                                | rved                   |                  | 0000 0000h                          | 0000 0000h                        | 0000 0000h                       |  |  |

| 3Ch      | MAX_LAT<br>[7:0] | MIN_GNT<br>[7:0]                    | IP[7:0]                | IL[7:0]          | <b>2A01 0100</b> h                  | <b>2A01 0100</b> h                | <b>1002 0100</b> h               |  |  |

| 40h      | rese             | erved                               | RETRY_<br>TIMEOUT      | TRDY_<br>TIMEOUT | 0000 <b>8000</b> h                  | 0000 <b>8000</b> h                | 0000 <b>8000</b> h               |  |  |

| Enhanced | Host Controlle   | er-specific PCI                     | registers              |                  |                                     |                                   |                                  |  |  |

| 60h      | PORTWAK          | ECAP[15:0]                          | FLADJ[7:0]             | SBRN[7:0]        | -                                   | -                                 | <b>0007 20</b> 20h               |  |  |

| Power ma | inagement regi   | sters                               |                        |                  |                                     |                                   |                                  |  |  |

| DCh      | PMC              | [15:0]                              | NEXT_ITEM_<br>PTR[7:0] | CAP_ID[7:0]      | D282 0001h                          | D282 0001h                        | FE82 0001h                       |  |  |

| E0h      | DATA[7:0]        | PMCSR_BSE<br>[7:0]                  | PMCS                   | R[15:0]          | 0000 <b>XX00</b> h <mark>[2]</mark> | 0000 <b>XX00</b> h <sup>[2]</sup> | 0000 <b>XX00</b> h <sup>[2</sup> |  |  |

## Table 3. PCI configuration space registers of OHCI1, OHCI2 and EHCI ... continued

[1] Reset values that are highlighted (for example, **0**) indicate read and write accesses; and reset values that are not highlighted (for example, 0) indicate read-only.

[2] See <u>Section 8.2.3.4</u>.

The HCD does not usually interact with the PCI configuration space. The configuration space is used only by the PCI enumerator to identify the USB Host Controller and assign appropriate system resources by reading the Vendor ID (VID) and the Device ID (DID).

## 8.2.1 PCI configuration header registers

The enhanced Host Controller implements normal PCI header register values, except the values for the memory-mapping base address register, serial bus number and device ID.

#### 8.2.1.1 Vendor ID register

This read-only register identifies the manufacturer of the device. PCI Special Interest Group (PCI-SIG) assigns valid vendor identifiers to ensure the uniqueness of the identifier. The bit description is shown in Table 4.

|         | VID - Vend<br>* reset value | lor ID regi | ster (add | Iress 00h) bit description                                                                              |

|---------|-----------------------------|-------------|-----------|---------------------------------------------------------------------------------------------------------|

| Bit     | Symbol                      | Access      | Value     | Description                                                                                             |

| 15 to 0 | VID[15:0]                   | R           | 1131h*    | <b>Vendor ID</b> : This read-only register value is assigned to NXP Semiconductors by PCI-SIG as 1131h. |

# 8.2.1.2 Device ID register

This is a 2-byte read-only register that identifies a particular device. The identifier is allocated by NXP Semiconductors. Table 5 shows the bit description of the register.

| Table 5.         DID - Device ID register (address 02h) bit description           Legend: * reset value |           |        |               |                                                                                                                                                                                                                                           |  |  |  |

|---------------------------------------------------------------------------------------------------------|-----------|--------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit                                                                                                     | Symbol    | Access | Value         | Description                                                                                                                                                                                                                               |  |  |  |

| 15 to 0                                                                                                 | DID[15:0] | R      | X* <u>[1]</u> | <b>Device ID</b> : This register value is defined by NXP Semiconductors to identify the Hi-Speed USB Host Controller IC product. For the ISP1562, NXP Semiconductors has defined OHCI functions as 1561h, and the EHCI function as 1562h. |  |  |  |

[1] X is 1561h for OHCI1 and OHCI2; X is 1562h for EHCI.

#### 8.2.1.3 Command register

This is a 2-byte register that provides coarse control over the ability of a device to generate and respond to PCI cycles. The bit allocation of the Command register is given in <u>Table 6</u>. When logic 0 is written to this register, the device is logically disconnected from the PCI bus for all accesses, except configuration accesses. All devices are required to support this base level of functionality. Individual bits in the Command register may or may not support this base level of functionality.

|        |       |     | . ,   |                    |     |     |      |       |

|--------|-------|-----|-------|--------------------|-----|-----|------|-------|

| Bit    | 15    | 14  | 13    | 12                 | 11  | 10  | 9    | 8     |

| Symbol |       |     | reser | ved <sup>[1]</sup> |     |     | FBBE | SERRE |

| Reset  | 0     | 0   | 0     | 0                  | 0   | 0   | 0    | 0     |

| Access | R/W   | R/W | R/W   | R/W                | R/W | R/W | R/W  | R/W   |

| Bit    | 7     | 6   | 5     | 4                  | 3   | 2   | 1    | 0     |

| Symbol | SCTRL | PER | VGAPS | MWIE               | SC  | BM  | MS   | IOS   |

| Reset  | 0     | 0   | 0     | 0                  | 0   | 0   | 0    | 0     |

| Access | R     | R/W | R     | R/W                | R   | R/W | R/W  | R/W   |

|        |       |     |       |                    |     |     |      |       |

#### Table 6. CMD - Command register (address 04h) bit allocation

[1] The reserved bits should always be written with the reset value.

| Bit      | Symbol   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 to 10 | reserved | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9        | FBBE     | Fast Back-to-Back Enable: This bit controls whether a master can do fast back-to-back transactions to various devices. The initialization software must set this bit if all targets are fast back-to-back capable.                                                                                                                                                                                                                                                                                                                       |

|          |          | 0 — Fast back-to-back transactions are only allowed to the same agent (value after RST#).                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |          | 1 — The master is allowed to generate fast back-to-back transactions to different agents.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8        | SERRE    | <b>SERR# Enable</b> : This bit is an enable bit for the SERR# driver. All devices that have an SERR# pin must implement this bit. Address parity errors are reported only if this bit and the PER bit are logic 1.                                                                                                                                                                                                                                                                                                                       |

|          |          | 0 — Disable the SERR# driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|          |          | 1 — Enable the SERR# driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7        | SCTRL    | <b>Stepping Control</b> : This bit controls whether a device does address and data stepping. Devices that never do stepping must clear this bit. Devices that always do stepping must set this bit. Devices that can do either, must make this bit read and write, and initialize it to logic 1 after RST#.                                                                                                                                                                                                                              |

| 6        | PER      | <b>Parity Error Response</b> : This bit controls the response of a device to parity errors. When the bit is set, the device must take its normal action when a parity error is detected. When the bit is logic 0, the device sets DPE (bit 15 in the Status register) when an error is detected, but does not assert PERR# and continues normal operation. The state of this bit after RST# is logic 0. Devices that check parity must implement this bit. Devices are required to generate parity, even if parity checking is disabled. |

| 5        | VGAPS    | VGA Palette Snoop: This bit controls how VGA compatible and graphics devices handle accesses to VGA palette registers.                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          |          | 0 — The device must treat palette write accesses like all other accesses.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |          | 1 — Palette snooping is enabled, that is, the device does not respond to palette register writes<br>and snoops data.                                                                                                                                                                                                                                                                                                                                                                                                                     |

|          |          | VGA compatible devices must implement this bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4        | MWIE     | Memory Write and Invalidate Enable: This is an enable bit for using the Memory Write and Invalidate command.                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          |          | 0 — Memory writes must be used instead. State after RST# is logic 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|          |          | <ol> <li>Masters may generate the command.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          |          | This bit must be implemented by master devices that can generate the Memory Write and Invalidate command.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3        | SC       | Special Cycles: Controls the action of a device on special cycle operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          |          | 0 — Causes the device to ignore all special cycle operations. State after RST# is logic 0.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          |          | <ol> <li>Allows the device to monitor special cycle operations.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2        | BM       | Bus Master: Controls the ability of a device to act as a master on the PCI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |          | 0 — Disables the device from generating PCI accesses. State after RST# is logic 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |          | <ol> <li>Allows the device to behave as a bus master.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1        | MS       | Memory Space: Controls the response of a device to memory space accesses.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |          | 0 — Disables the device response. State after RST# is logic 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          |          | 1 — Allows the device to respond to memory space accesses.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0        | IOS      | IO Space: Controls the response of a device to I/O space accesses.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |          | 0 — Disables the device response. State after RST# is logic 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          |          | 1 — Allows the device to respond to I/O space accesses.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### Table 7. CMD - Command register (address 04h) bit description

#### 8.2.1.4 Status register

The Status register is a 2-byte read-only register used to record status information on PCI bus-related events. For bit allocation, see Table 8.

| Table 8. | STATUS - Status register (address 06h) bit allocation |

|----------|-------------------------------------------------------|

|----------|-------------------------------------------------------|

| Bit    | 15   | 14       | 13   | 12  | 11  | 10    | 9        | 8    |

|--------|------|----------|------|-----|-----|-------|----------|------|

| Symbol | DPE  | SSE      | RMA  | RTA | STA | DEVSE | ELT[1:0] | MDPE |

| Reset  | 0    | 0        | 0    | 0   | 0   | 0     | 1        | 0    |

| Access | R    | R        | R    | R   | R   | R     | R        | R    |

| Bit    | 7    | 6        | 5    | 4   | 3   | 2     | 1        | 0    |

| Symbol | FBBC | reserved | 66MC | CL  |     | rese  | rved     |      |

| Reset  | 0    | 0        | 0    | 1   | 0   | 0     | 0        | 0    |

| Access | R    | R        | R    | R   | R   | R     | R        | R    |

| Table 9. | <b>STATUS - Status</b> | register  | address 06h   | ) bit description |

|----------|------------------------|-----------|---------------|-------------------|

| 10010 01 | entree etatao          | i ogiotoi | 14441000 0011 |                   |

| Table 5. | UIAIUU           | Status register (address bon) bit description                                                                                                                                                                                                                                                                 |

|----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit      | Symbol           | Description                                                                                                                                                                                                                                                                                                   |

| 15       | DPE              | <b>Detected Parity Error</b> : This bit must be set by the device whenever it detects a parity error, even if the parity error handling is disabled.                                                                                                                                                          |

| 14       | SSE              | <b>Signaled System Error</b> : This bit must be set whenever the device asserts SERR#. Devices that never assert SERR# do not need to implement this bit.                                                                                                                                                     |

| 13       | RMA              | <b>Received Master Abort</b> : This bit must be set by a master device whenever its transaction, except for special cycle, is terminated with master abort. All master devices must implement this bit.                                                                                                       |

| 12       | RTA              | <b>Received Target Abort</b> : This bit must be set by a master device whenever its transaction is terminated with target abort. All master devices must implement this bit.                                                                                                                                  |

| 11       | STA              | <b>Signaled Target Abort</b> : This bit must be set by a target device whenever it terminates a transaction with target abort. Devices that never signal target abort do not need to implement this bit.                                                                                                      |

| 10 to 9  | DEVSELT<br>[1:0] | <b>DEVSEL Timing</b> : These bits encode the timing of DEVSEL#. There are three allowable timing to assert DEVSEL#:                                                                                                                                                                                           |

|          |                  | 00b — Fast                                                                                                                                                                                                                                                                                                    |

|          |                  | 01b — Medium                                                                                                                                                                                                                                                                                                  |

|          |                  | <b>10b</b> — Slow                                                                                                                                                                                                                                                                                             |

|          |                  | 11b — Reserved                                                                                                                                                                                                                                                                                                |

|          |                  | These bits are read-only and must indicate the slowest time that a device asserts DEVSEL# for any bus command, except Configuration Read and Configuration Write.                                                                                                                                             |

| 8        | MDPE             | <b>Master Data Parity Error</b> : This bit is implemented by bus masters. It is set when the following three conditions are met:                                                                                                                                                                              |

|          |                  | <ul> <li>The bus agent asserted PERR# itself, on a read; or observed PERR# asserted, on a write.</li> </ul>                                                                                                                                                                                                   |

|          |                  | <ul> <li>The agent setting the bit acted as the bus master for the operation in which error occurred.</li> </ul>                                                                                                                                                                                              |

|          |                  | <ul> <li>PER (bit 6 in the Command register) is set.</li> </ul>                                                                                                                                                                                                                                               |