ProASICLUS系列设备,即Actel的第二代Flash fpga,在Actel的ProASIC系列上提供了增强的性能。它结合了asic的优点和可编程设备的优点,通过非易失性闪存技术。这使得工程师能够使用现有的ASIC或FPGA设计流程和工具创建高密度系统。此外,ProASICELu§系列提供了一种基于两个车载锁相环(PLLs)的独特时钟调节电路。

该系列提供多达100万个系统闸,支持最多198 kbits的双端口SRAM和最多712个用户I/Os,所有提供50 MHz PCI性能优势,为设计者提供超越性能的扩展。与基于sram的fpga不同,路由层次的四层简化了路由,而Flash技术的使用允许在powerup上实时运行所有功能。支持设备编程不需要外部引导PROM。虽然机载安全机制阻止访问项目信息,但可以在系统内进行重新编程,以支持未来的设计迭代和现场升级。

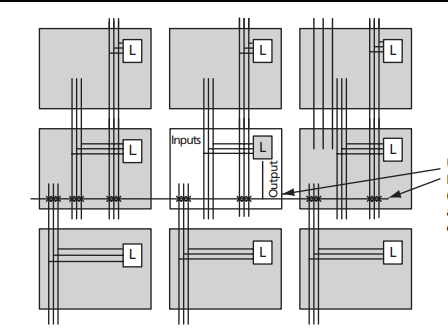

该设备的体系结构减轻了ASIC迁移的复杂性在较高的用户量。这使得ProASICPLUs成为网络、通信、计算和航空电子市场应用的有效解决方案ProASICPLUS系列通过具有四层金属层的基于advanced flash的0.22 um LVCMOS流程来实现其非挥发性和可编程性。标准的CMOS设计技术被用来实现逻辑和控制功能,包括LLs和LVPECL输入。这导致了可预测的性能兼容门阵列。ProASICPLUs架构提供了与门阵列相当的粒度。该设备的核心由一块磁砖组成。每个tile都可以配置为触发器。闩锁,或通过编程适当的闪光开关的三输入输出逻辑功能。的细粒度、灵活的路由资源和丰富的Flash交换机的组合允许100%的利用率和超过95%的可路由性用于高度拥挤的设计。

Tiles和更大的功能通过一个四层路由层次结构互连。嵌入式双端口SRAM块与内置的FIFO/RAM控制逻辑可以有用户定义的深度和宽度。用户还可以选择同步或异步操作编程,以及奇偶校验代或校验。每个装置中独特的时钟调节电路包括两个时钟调节模块。每个块提供锁相环核心、延迟线、相移(0和180)和时钟乘法器/分法器,以及需要提供到锁相环的双向访问的电路。PLL块包含四个可编程分频器,允许传入的时钟信号被从1到64的广泛范围的因素除。时钟调节电路也将输入的参考时钟提升到8 ns(增量0.25 ns)。锁相环在运行期间可以在内部或外部被确认,而无需重新设计或重新编程部件。除了PLL,还有两个LVPECL差分输入对,以适应高速时钟和数据输入。

为客户提供更全面、更低成本、更全面的测试。Actel的ProASICPLUS设备完全兼容IEEE标准1149.1的测试访问端口和边界扫描测试架构。有关Flash FPGA实现的更多信息,请参阅第1-11页的“边界扫描(标签)”部分。ProASICELUS设备可在各种高性能塑料包装。下面几节将更详细地描述上面讨论的那些包和性能特性。