XC7VX690T-2FFG1761I赛灵思芯片描述:

西安福川电子科技拥有此芯片的优势渠道。质保原装正品,如您需要此芯片,可点击右侧在线客服沟通,或直接致电我司。

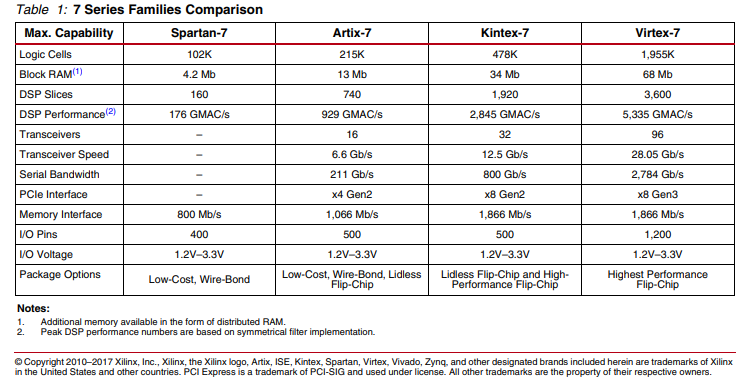

Xilinx@7系列FPGA由四个FPGA家族组成,解决了系统的完整需求,从低成本,小的形式因素。对成本敏感,高容量的应用程序,超高端连接带宽,逻辑容量,信号处理能力,最苛刻的高性能应用程序。7系列FPGAs包括斯巴达7系列:实现了低成本、低功耗和hiat功能kintex -7系列:为最佳性价比而优化的性能。

有低成本,非常小的外形因素与上一代相比的改进,产生了一个新的类packaaina用于最小的PCB聚焦器。或 Fpgas 。Artix@-7系列:优化的低功耗应用需要串行Virtex-7系列:优化的最高系统性能和收发器和高DSP和逻辑吞吐量。提供最低的容量提高2倍的系统性能。最高高吞吐量的总材料成本,成本敏感由堆叠硅互连(SSl)启用的功能设备应用程序。技术建立在最先进的,高性能,低功耗(HPL), 28nm,高k金属栅(HKMG)工艺技术。7系列fpga能够以2.9 Tb/s的IO带宽实现系统性能的空前提高。200万电池电容,5.3/秒DSP。与上一代设备相比,consumina降低了50%的功率,从而为ASSPs和ASICs提供了一个完全可靠的替代品。

混合模式时钟管理器和锁相环路MMCM和PLL有许多共同的特点。两者都可以作为一个频率合成器的广泛范围的频率和作为传入时钟的抖动滤波器。在两个组件的中心是一个电压控制振荡器(VCO),它根据从相位频率检测器(PFD)接收的输入电压来加速和减速分频器有三种:D. M.和O.预分频器D(可通过配置编程,后通过DRP编程)降低了传统锁相锁相频比较器的输入频率,并提供了一个输入信号。

反馈分配器M(可通过配置编程,然后通过DRP编程)作为一个乘法器,因为在给相比较器的其他输入端之前,反馈分配器先将压控振荡器输出的频率除掉。D和M必须选择适当,以保持VCO在其规定的频率范围内。VCO有八个等间隔的输出相位每一个都可以被选择去驱动一个输出分频器(六个为锁相环)。MMCM和PLL有三种输入-发送滤波器选项:低带宽、高带宽或优化模式,而不是最小的相位偏移。高带宽模式有最好的相位偏移,但不是最好的分路器衰减。优化模式允许工具找到最好的设置。

MMCM附加可编程功能MMCM可以有一个分数计数器在反馈路径(作为一个乘法器)或在一个输出路径。分频计数器允许1/8的非整数增量,因此可以增加8倍的频率合成能力。该MMCM还可以提供固定或动态相移的小增量,这取决于VCO频率。在1600mhz时,相移定时增量为11.2 ps。

时钟分布每个7系列FPGA提供六种不同类型的时钟线(BUFG)。布尔,BUFIO。BUEH, BUFMB,和高性能时钟),以解决不同的时钟要求的高扇出,短传播delav,和极低的歪斜。全局时钟线在每个7系列FPGA(除了XC7S6和XC7S15)中,32条alobal时钟线具有最高的扇面,可以到达每个触发器时钟、时钟启用、时钟设置以及许多逻辑输入。在由水平时钟缓冲器(BUEH)驱动的任何时钟寄存器中有12条全球时钟线,每个BUFH可以独立启用/禁用,允许在一个区域内关闭时钟,从而提供了对哪个时钟消耗电力的精细控制。

全局时钟线可以由全局时钟缓冲器驱动,也可以执行无小故障时钟多路复用和时钟启用功能。全球时钟通常由CMT驱动,可以完全消除基本的时钟分配延迟。一个区域被定义为一个区域是50 //O和50 CLB高和一半的芯片宽。7系列FPGAs有两个和24个区域。在每个实数有四个区域时钟轨道,每个区域时钟缓冲器可以从四个时钟能力的输入引脚的任何驱动,它的频率可以选择性地被从1到8的任何整数除.