一般的描述

CS5012A/14/16是12、14和16位单片模拟到数字转换器,转换时间为7.2us、14.25us和16.25us。独特的自校准电路,确保优良的线性度和微分非线性,没有丢失的代码。偏移量和满刻度误差保持在1/2 LSB (CS5012A/14)和1 LSB (CS5016),无需校准。单极和双极输入范围是数字选择兼容CS5012A/14/16的大头针由一个DAC组成。转换和校准微控制器,振荡器。

比较器。微处理器兼容三态VO和校准电路。输入跟踪-保持,固有的器件的采样结构,获得输入信号后每次转换使用快速回转片上缓冲放大器。这允许吞吐量高达100 kHz (CS5012A)、56 kHz (CS5014)和50 kHz (CS5016)有一个评估板(CDB5012/14/16),可以快速评估ADC的性能。

操作理论Cs5012A/14/16系列使用逐次逼近转换技术。将模拟输入与由转换算法控制的D/ a转换器的输出进行连续比较。逐次逼近首先将模拟输入与DAC输出进行比较,DAC的输出被设置为半比例(MSB打开,所有其他比特断开)。如果发现输入小于一半刻度,MSB将被重置为零,并将输入与四分之一刻度比较(下一个MSB打开)。其他所有人)。如果投入超过一半规模,MSB将保持高,下一次比较将是全规模的四分之三。这个过程一直持续到所有位都被执行完毕。

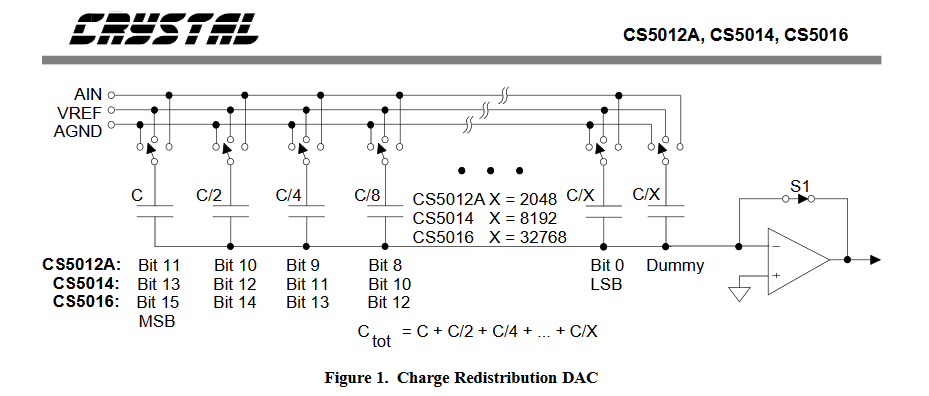

与传统的电阻网络不同,DAC是一组二进制加权电容器。阵列中的所有电容器在比较器的输入端共用一个节点。他们的其他终端是能够被连接到AIN, AGND,或VREF(图1)。当设备不校准或转换,所有的电容器被绑定到AIN形成Ctot。开关Sl被关闭,阵列上的电荷Qin跟踪输入信号Vin(图2a)。

当发出转换命令时,打开开关Sl,如图2b所示。这个陷阱电荷秦在比较器的一侧电容阵列和创建一个浮动节点在比较器的输入。转换算法操作在这个固定的电荷,和信号在模拟输入管脚被忽略。实际上,整个DAC电容阵列充当模拟存储器.

| 型号 | #订货代码 |

| XTREME | 5012-TD12B |

| XTREME | 5012-TE12B |

| XTREME | 5014-SD14B |

| XTREME | 5014-SE14B |

| XTREME | 5014-TD14B |

| XTREME | 5014-TE14B |

| XTREME | 5016-SD16B |

| XTREME | 5016-SE16B |

| XTREME | 5016-TD16B |

| XTREME | 5016-TE16B |

| XTREME | 5101A-SD8B |

| XTREME | 5101A-SE8B |

| XTREME | 5101A-TD8B |

| XTREME | 5101A-TE8B |

| XTREME | 5102A-SDB |

| XTREME | 5102A-SEB |

| XTREME | 5102A-TDB |

| XTREME | 5102A-TEB |