介绍

Lattice的高性能ispMACH 4000ZE系列提供了超低功耗CPLD解决方案。新家族基于莱迪思行业领先的ispMACH 4000架构。保留上一代的精华。ispMACH 4000ZE架构专注于在灵活的CPLD家族中结合高性能和低功耗的重大创新。例如,家庭的新电源保护功能,通过防止最大限度地减少动态功耗由于不必要的I/O引脚活动而导致的内部逻辑切换ispMACH 4000ZE结合了高速和低功率与易于设计所需的灵活性。

凭借其健壮的全局路由池和输出路由池,该系列提供了出色的首次拟合度、时序可预测性、路由、引脚输出保留和密度迁移ispMACH 4000ZE系列提供的宏单元密度范围从32到256。在Thin Quad Flat Pack (TOFP)、Chip Scale BGA (csBGA)和Ultra Chip Scale BGA (ucBGA)封装中有多种密度-/0组合,范围从32到144个pin /balls。表1显示了宏单元格、包和I/O选项以及其他关键参数用户可编程的内部振荡器和定时器包括在设备的任务,如LED控制,键盘扫描器和类似的管家型状态机。为了节省电能,可以选择禁用此功能。ispMACH 4000ZE系列具有增强的系统集成能力。

支持1.8V供电电压和3.3V供电电压。2.5V, 1.8V和1.5V接口电压。此外,当I/O组配置为3.3V操作时,输入可以安全驱动到5.5V,使该系列能够容忍5V。ispMACH 4000ZE还提供增强的VO功能,如转换率控制,PCI兼容性,总线保持闩锁,上拉电阻,下拉电阻开路漏输出和热插接。上拉、下拉和总线控制功能在“每个针”的基础上是可控的。ispMACH 4000ZE家族成员通过IEEE标准1532接口在系统中可编程1.8V。您可以直接咨询福川电子进行咨询。

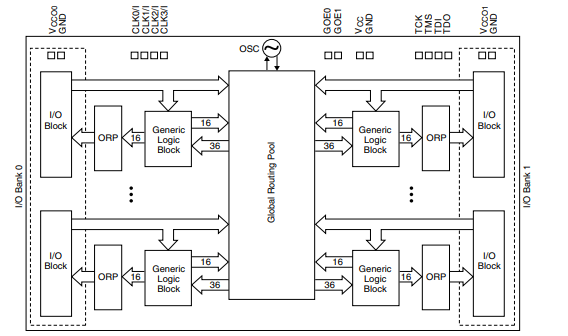

IEEE标准1149.1边界扫描测试能力也允许在自动化测试设备上进行产品测试。1532接口信号TCK。TMS、TDI和TDO参考Vcc(逻辑核)概述ispMACH 4000ZE设备由多个36输入、16 macrocell通用逻辑块(glb)组成,由一个全局路由池(GRP)连接。输出路由池(ORPs)将glb连接到I/O块(IOBs), IOBs包含多个VO单元。

其他系列产品推荐

| LC4032V-75TN48I | Lattice |

| LC4032ZC-35TN48C | Lattice |

| LC4032ZC-5MN56C | Lattice |

| LC4032ZC-5MN56I | Lattice |

| LC4032ZC-5TN48C | Lattice |

| LC4032ZC-5TN48I | Lattice |

| LC4032ZC-75MN56I | Lattice |

| LC4032ZC-75TN48C | Lattice |

| LC4032ZC-75TN48E | Lattice |

| LC4032ZC-75TN48I | Lattice |

| LC4032ZE-4MN64C | Lattice |

| LC4032ZE-4TN48C | Lattice |

| LC4032ZE-5MN64C | Lattice |

| LC4032ZE-5TN48C | Lattice |

| LC4032ZE-5TN48I | Lattice |

| LC4032ZE-7MN64C | Lattice |

| LC4032ZE-7MN64I | Lattice |

| LC4032ZE-7TN48C | Lattice |

| LC4032ZE-7TN48I | Lattice |

| LC4064V-10TN100I | Lattice |

| LC4064V-10TN44I | Lattice |