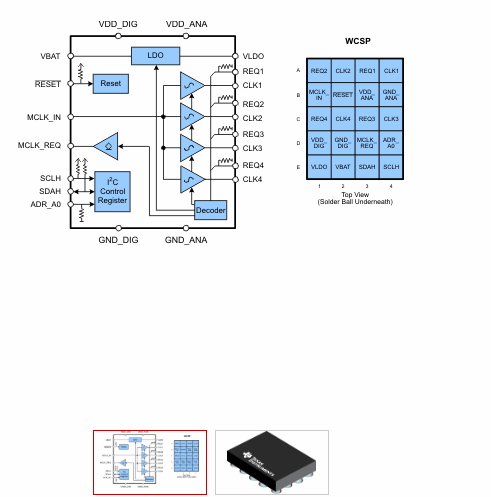

CDC3S04 是一款四通道低功耗低抖动正弦波时钟缓冲器。它可用于将单个主时钟缓冲到多个外设。四个正弦波输出 (CLK1–CLK4) 设计用于最小化通道间偏移和超低附加输出抖动。

每个输出都有自己的时钟请求输入,用于启用专用时钟输出。这些时钟请求是高电平有效(也可以通过 I 2 C更改为低电平有效),并生成一个输出信号,可以将其发送回主时钟以请求时钟 (MCLK_REQ)。MCKL_REQ 是开源输出,支持线或功能(默认模式)。它需要一个外部下拉电阻。MCKL_REQ 可通过 I 2 C更改为线与或推挽功能。

CDC3S04 还提供一个 I 2 C 接口(Hs 模式),可用于启用或禁用输出、选择 REQ 输入的极性以及允许控制内部解码。

CDC3S04 具有片上高性能 LDO,可接受 2.3V 至 5.5V 的电压并输出 1.8V 电源。该 1.8V 电源可用于为外部 1.8V TCXO 供电。它可以在 TCXO 上启用或禁用以实现节能。

RESET输入端的低信号将输出 CLK1 和 CLK4 切换到默认状态。在此配置中,CLK1 和 CLK4 为 ON(参见 );其余设备功能不受影响。此外,RESET输入提供了一个毛刺滤波器,可抑制RESET线上典型的 300 ns 尖峰,以保留错误复位。可以通过 V DD_DIG的上电周期启动完整的器件复位到默认条件。

CDC3S04 由两个 1.8V 电源供电。内核逻辑有一个内核电源 (VDD_DIG/GND_DIG),正弦波输出有一个低噪声模拟电源 (VDD_ANA/GND_ANA)。CDC3S04 专为无序列加电而设计。可以以任何顺序施加两个电源电压。

CDC3S04 采用 0.4 毫米间距 WCSP 封装(1.6 毫米 × 2 毫米),并针对低待机电流 (0.5 µA) 进行了优化。它的特点是在 –40°C 至 85°C 的温度范围内工作。

1:4 低抖动时钟缓冲器

单端正弦波时钟输入和输出

超低相位噪声和待机电流

每个输出的独立时钟请求输入

用于低噪声 TCXO 电源的片上低压降输出 (LDO)

串行 I 2 C 接口(兼容高速模式,

3.4 Mbit/s)

1.8V 设备电源

宽温度范围,–40°C 至 85°C

ESD 保护:2 KV HBM、750 V CDM 和 100 V MM

小型 20 引脚芯片级封装:0.4 毫米间距 WCSP(1.6 毫米 × 2 毫米)