特征

一个差分(LVPECL、LVDS、HCSL或CML)输入对分配给两个LVPECL输出对

将任何单端输入信号转换为3.3 V LVPECL电平,在输入端有电阻偏置

ω20 ps最大输出到输出偏斜

ω480 ps最大传播延迟

7.0.15PS最大加性RMS相位抖动在156.25 MHz(12 kHz至20 MHz偏移)

高达1.5GHz的操作

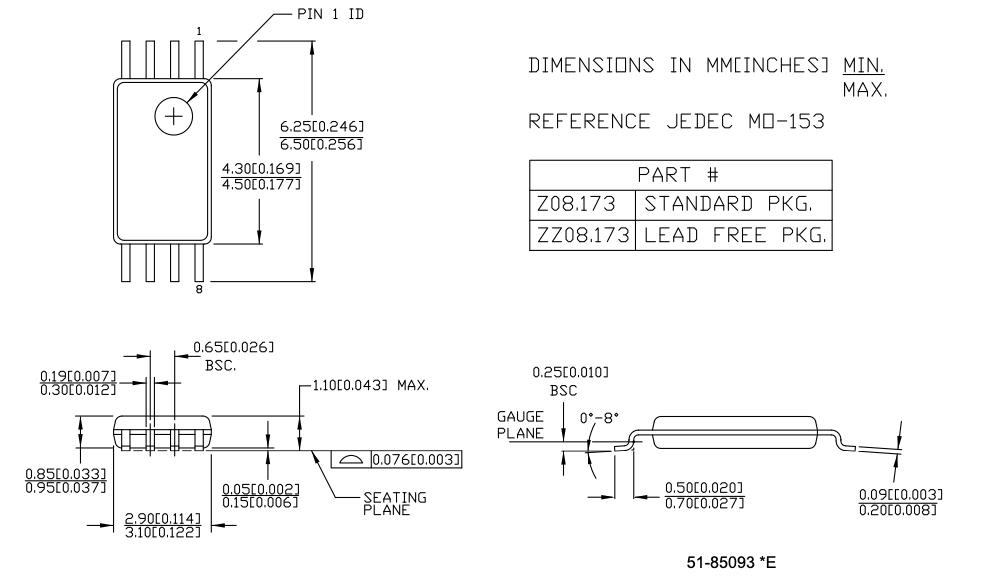

8针SOIC或8针TSSOP封装

2.5-V或3.3-V工作电压[1]

商业和工业运行温度范围

逻辑框图

CY2DP1502型

1: 2 LVPECL扇出缓冲区

功能描述

CY2DP1502是一种超低噪声、低偏斜、低传输延迟1:2的LVPECL扇形输出缓冲器,旨在满足高速时钟分布应用的要求。该器件具有全差分内部结构,优化后可在高达1.5ghz的工作频率下实现低附加抖动和低偏斜。

应用程序信息

CY2DP1502可以通过偏置互补输入时钟(INx)与单端CMOS输入一起使用。差分输入对的“真”输入引脚(INx)可由单端CMOS输入信号馈送。同一差分输入对的“互补”输入引脚(INx#)可以用Vref偏置。

图9显示了可用于向CY2DP1502提供单端CMOS输入的示意图。

基准电压Vref=VDD/2由偏置电阻器R1、R2和电容器C0产生。该偏置电路应尽可能靠近输入引脚。可能需要调整R1和R2的比率,以将Vref定位在输入电压摆动的中心。例如,如果输入时钟摆幅为2.5 V,VDD=3.3 V,则Vref应为1.25 V,R2/R1=0.609。

CY2DP1502SXIT

CY2DP1502ZXI

CY2DP1502ZXIT

CY2DP1504ZXC

CY2DP1504ZXCT

CY2DP1504ZXI

CY2DP1504ZXIT

CY2DP1510AXC

CY2DP1510AXCT

CY2DP1510AXI

CY2DP1510AXIT

CY2DP814ZXC

CY2DP814ZXCT

CY2X0137FLXCT

CY2X0137FLXIT

CY2X013FLXIT

CY2X0147FLXCT

CY2X0147FLXIT

CY2X014FLXIT

CY2X014LXI011T

CY2XF23LXC001T

CY2XF24LXI009T

CY2XF327FLXCT

CY2XF327FLXIT

CY2XF32FLXIT

CY2XF33LXC533T

CY2XL11ZXC

CY2XL11ZXCT

CY2XL12ZXC05

CY2XL12ZXC05T

CY2XL12ZXI03

CY2XL12ZXI03T

CY2XL12ZXIC04

CY2XL12ZXIC04T

CY2XP22ZXI

CY2XP22ZXIT

CY2544FIT

CY2545C009

CY2545C009T

CY2545C010

CY2545C010T

CY2545C020

CY2545C020T

CY2545C022

CY2545C022T

CY2545FC

CY2545FCT

CY25482SXC-008

CY25482SXC-008T

CY2548C004

CY2548C004T