西安福川电子科技的IDT70V35/34 (DT70V25/24)是一个高速B/4K x18 (8/4K x16)双端口静态RAM。IDT70V35/34 (IDT70V25/24)被设计用来作为一个独立的双端口RAMor,作为36位(32位)或更广泛的存储系统应用的一个主/从双端口RAM的组合,结果在全速,无错误操作,不需要额外的离散逻辑。这个设备提供了两个独立的端口与独立的控制,地址,和允许独立的IO针,异步访问读或写内存的任何位置。

自动断电由CE控制的特性允许每个端口的片上电路进入一个非常低的待机电源模式。使用idt 'sCMOS高性能技术制造,这些设备通常仅使用430mW (IDT70V35/34)和400mW (IDT70V25/24)的功率IDT70V35/34 (DT70V25/24)采用100-pir塑料包装瘦四Flatpack。idt70v25 /24采用陶瓷84-pir包装PGA和84针PLCC。

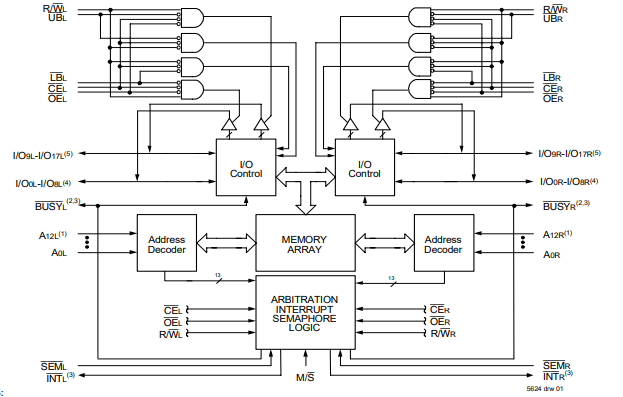

功能描述IDT70V35/34 (IDT70V25/24)提供了两个端口的分离控制,地址和/O引脚,允许独立访问读写sc写入内存的任何位置。IDT70V35/34 (IDT70V25/24)具有CE控制的自动关机功能。CE控制在芯片电源下的电路,允许各自的端口qo进入。待机模式时,不选择(CE高)。当端口是enablec时,允许访问整个内存数组中断如果用户选择中断功能,每个端口将分配一个memorylocation (mail bo或message center)。

当右端口写入内存位置1FFI(十六进制)(FE用于IDT70V34和IDT70V24)时,断言左portinterrupt fla (INTL),其中写入是根据每个真值表定义的CER -R/ wrl - vin。leftport通过地址位置1FFE (FFEfo IDT70V34和IDT70V24)访问whencel - oel - vl来清除IDT70V35和IDT70V25上的交叉。RWLisa“不关心”。同样,当leftipo为IDT70V35和IDT70V25 (HEX)写入memorylocation 1FFF(为IDT70V34和IDT70V24写入FFI)时,正确的portinterrupt flaq (INTn)被设置,为了清除中断标志(INTe),正确的端口必须为IDT70V35和IDT70V25读取内存位置1FFF(为IDT70V34和IDT70V24读取FFF)。

消息(IDT70V35和IDT70V25在1FFE或1FFF (FFE或FFF fo IDT70V34和IDT70V24)是用户定义的,因为它是一个addressabl SRAMlocation。如果他不使用中断功能,地址位置1EFI和1FFF forIDT70V35和IDT70V25 (FFE和FFF为IDT70V34和IDT70V24)不是作为邮箱使用,而是作为随机存储器的一部分。中断操作请参考真值表Ill。