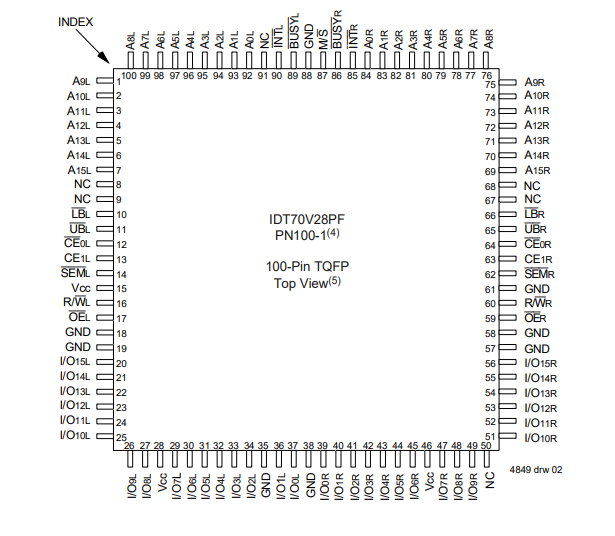

描述IDT70V28是一个高速64K x 16双端口静态RAM。IDT70V28被设计用来作为一个独立的1024k位双端口RAM或作为一个32位或更多字系统的主/从双端口组合RAM。在32位或更宽的内存系统应用中使用IDT主/从双端口RAM方法可以实现全速、无错误操作,而不需要额外的离散logio该设备提供了两个独立的端口与独立的控制,地址,和VO引脚,允许独立,异步访问.

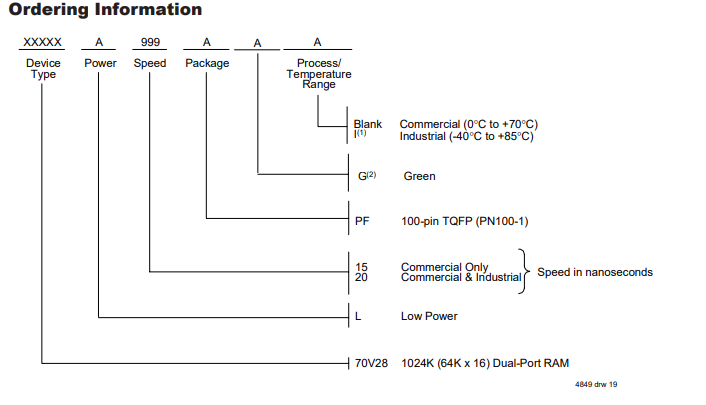

用于对内存中的任何位置进行读写。由芯片控制的自动断电功能使(CEo或CE)允许每个端口的芯片电路进入一个非常低的待机电源模式。采用IDT的CMOS高性能技术制造的这些设备通常只需要440mW的功率IDT70V28被包装在一个100针薄的四平板(TOFP)。

注:1. 所有地址转换期间的RMW或CE或DE和LE= VH。2. 一个wite发生在A E v的过载(ew或twe)和一个记忆周期的RN= Vi。3.红外光谱是从cer RN(或SEM或r /M)早期到写入周期结束时测量的。4. 在此期间,IO引脚在输出状态和输入信号必须不应用。5. 当CE或SEM Vi跃迁与NMV Wu跃迁同时发生或发生在NMV Wu跃迁之后,outut reman处于光阻抗状态6. Tming取决于哪个激活信号是最后断言的,E还是RM。7. 此参数由设备特性保证,但未经过生产测试。过渡是测量OmV从稳态输出测试负载(Fiqure 2)。在RW控制的写周期,写脉冲宽度必须是较大的tMp或(tz + tow),以降低两个驱动器关闭和数据被放置在总线上为请求的tow。如果E - ViH是在一个RW控制的写周期中,这个要求就不适用了,写程序可以像指定的那样短9. 对RAM、CE- ViL和SEM-进行访问,对信号量、CE- ViH和SEM- VL进行访问。任何一种条件都必须满足tew。10. 参考真值表1芯片启用。