描述

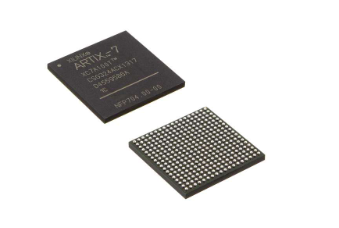

Xilinx@7系列FPGA由四个FPGA家族组成,解决了从低成本、小形式因素等完整的系统需求。对成本敏感的,高分辨率的应用,以超hiah端连接带宽,loaic容量,和信号处理能力为最需求的高性能应用。7系列fpga包括:Spartan@-7系列:优化为低成本,低功耗,高Kintex@-7 Familv:优化了2x的最佳性价比VO性能,可在低成本,非常小的形式facton与上一代相比有了改进,启用了一个新类封装最小的PCB占地面积或 Fpgasarticle -7家族:优化的低功耗应用需要串行VirtexB-7系列:为最高的系统性能和收发器和hiah DSP和loaic贯穿,提供最低容量,系统性能提升2倍。最高高通量,成本敏感的材料总成本堆叠硅互连(SSI)使能的能力设备应用程序技术。基于最先进的、高性能、低功耗(HPL)、28 nm、高k金属栅(HKMG)工艺技术,7系列fpga实现了在2.9 Tb/s IO带宽下无与伦比的系统性能提升。

200万loaic电池容量。5.3 TMAC/s DSP。与上一代设备相比,耗电量减少50%,为ASSPs和ASICe提供了一个完全可编程的替代方案7系列FPGA特性总结先进的高性能FPGA逻辑基于真实的6输入查找表(LUT技术可作为分布式内存共享)。36kb双端口块RAM内置FIFO逻辑片上数据缓冲。高性能的选择技术,支持高达1.866 Mhs的DDRa接口高速串行连接,内置千兆收发器,最大速率从600 Mb/s到6.6 Gb/s到28.05 Gb/s。提供特殊的低功耗模式,为芯片对芯片接口进行了优化onfiqable模拟接口(XADC),结合带有片上热传感器和供应传感器的12位1MSPS模拟-拨号转换器。

用户DSP片与25 x 18乘法器。48位累加器和hiah性能滤波器的预加器,包括优化的对称有效滤波强大的时钟管理块(CMT),结合锁相环(PLL)和混合模式时钟管理器(MMCM)块的高精度和低itter。PCI Express@ (PCle)集成块,用于最多x8 Gen3端点和根端口设计。广泛的配置选项,包括对商品存储器的支持,256位AES加密与HMAC/SHA-256认证,以及内置的SEU检测和校正。低成本,线连接,无盖子的flio芯片和高信号完整性flio芯片封装提供了在同一封装中的家庭成员之间容易迁移。所有包可用的Pb-free和Pb aption中选定的包。设计高性能和最低功耗的28nm。HKMG。HPL工艺,1.0V铁芯电压工艺技术v和0.9V铁芯间距选择更低的功率。

| XC4VSX55-10FFG1148I | XILINX |

| XC7VX690T-2FFG1761I | XILINX |

| XC7K480T-2FFG1156I | XILINX |

| XC7A100T-2CSG324I | XILINX |

| XC7Z020-2CLG484I | XILINX |

| XC7A200T-2FBG484I | XILINX |

| XC6SLX45-2FGG484I | XILINX |

| XC7Z045-2FFG900I | XILINX |

| XC7K325T-2FFG900I | XILINX |

| XC7K325T-2FFG676I | XILINX |

| XC7Z100-2FFG900I | XILINX |

| XCVU7P-2FLVC2104I | XILINX |