介绍

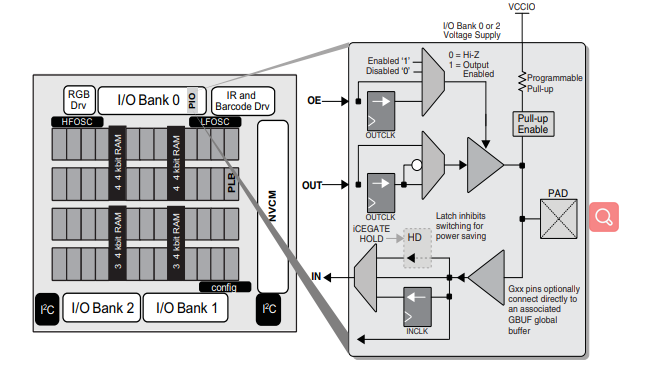

iCE40 UltraLite器件是在40nm CMOS低功率工艺上制造的。该器件结构具有用户可配置控制器和两个振荡器等特点iCE40 UltraLite FPGAs的体积非常小,小到1.409毫米× 1.409毫米。小巧的外形让该设备能够轻松地适应多种移动应用程序。表1-1显示了LUT密度,封装和I/O引脚计数。iCE40 UltraLite设备提供了VO功能,如可编程的多值上拉电阻。上拉功能在“每针”的基础上是可控的iCE40 UltraLite设备还提供灵活、可靠和安全的片上NVCM配置。

这些设备也可以从外部SPI闪存配置自己,或由外部主机配置,如aCPU。Lattice提供了多种设计工具,允许使用iCE40 UltraLite系列设备有效地实现复杂的设计。流行的逻辑合成工具为iCE40 UltraLite提供了合成库支持。晶格设计工具使用综合工具输出,以及用户指定的偏好和限制,在iCE40 UltraLite设备中放置和路由设计。这些工具从路由中提取时间,并将其反向注释到时间验证的设计中.

路由在iCE40 UltraLite设备中提供了许多资源来使用相关的控制信号单独路由信号。路由资源由交换电路、缓冲器和金属互连(路由)段组成。plb间连接使用三种不同类型的路由资源:邻接(跨越两个plb)、x4(跨越五个plb)和x12(跨越13个plb)。相邻、x4和x12连接在对角线、水平和垂直方向上提供快速和有效的连接。设计工具接收合成工具的输出,并确定设计的位置和路线。时钟/控制分销网络每个iCE40 UltraLite设备有6个全局输入,顶部有2个引脚,底部有4个引脚这些全局输入可以用作高扇出网、时钟、复位或使能信号。专用的全局引脚被识别为Gxx,每个引脚驱动8个全局缓冲器中的一个。全局缓冲区被标识为GBUF[7:0]。这六个输入可以作为通用I/O,如果他们不被用来驱动时钟网具体的全局缓冲区与PLB的输入之间的连接如表2-2所示。所有全局缓冲区可选地连接到PLB CLK输入。8个全局缓冲区中的任何4个都可以驱动逻辑输入到一个PLB。

偶数的全局缓冲区可选地驱动Set/Reset输入到一个PLB。类似地,奇数号缓冲区可选地驱动PLB时钟启用输入。GBUF[7:6, 3:0]可以分别直接连接到G[7:6, 3:0]引脚。GBUF4和GBUF5可以连接到两个片上振荡器(GBUF4连接到LFOSC, GBUF5连接到HFOSC)。

| 型号 | 品牌 |

| iCE40HX1K-CB132 | Lattice |

| iCE40HX1K-TQ144 | Lattice |

| iCE40HX1K-VQ100 | Lattice |

| ICE40HX4K-BG121 | Lattice |

| ICE40HX4K-BG121TR | Lattice |

| iCE40HX4K-CB132 | Lattice |

| iCE40HX4K-TQ144 | Lattice |

| ICE40HX8K-BG121 | Lattice |

| ICE40HX8K-BG121TR | Lattice |

| iCE40HX8K-CB132 | Lattice |

| iCE40HX8K-CM225 | Lattice |

| iCE40HX8K-CT256 | Lattice |

| ICE40LM1K-CM36 | Lattice |

| ICE40LM1K-SWG25TR50 | Lattice |

| ICE40LM2K-CM36 | Lattice |

| ICE40LM2K-SWG25TR50 | Lattice |

| ICE40LM4K-SWG25TR50 | Lattice |

| ICE40LP1K-CB121 | Lattice |

| iCE40LP1K-CB81 | Lattice |

| iCE40LP1K-CM121 | Lattice |

| iCE40LP1K-CM36 | Lattice |

| ICE40LP1K-CM36A | Lattice |

| iCE40LP1K-CM49 | Lattice |

| iCE40LP1K-CM49TR | Lattice |

| ICE40LP1K-CM49TR1K | Lattice |

| iCE40LP1K-CM81 | Lattice |

| iCE40LP1K-QN84 | Lattice |

| ICE40LP1K-SWG16TR1K | Lattice |

| ICE40LP1K-SWG16TR50 | Lattice |