iCE40设备上电复位电路,在上电和运行过程中监控Vcc、Vccio 2、Vpp 2V5和Vcc spl电压水平。通电时,POR电路监控Vcc、Vccio 2、Vpp 2v5和Vco spl(控制配置)电压水平。然后,在达到本数据表直流和开关特性部分的上电复位电压表中指定的上电级别后,触发从片上NVCM或外部闪存的下载。在配置之前和配置期间,IOs处于三态状态。一旦设备完成配置,IOs就会发布给用户功能。

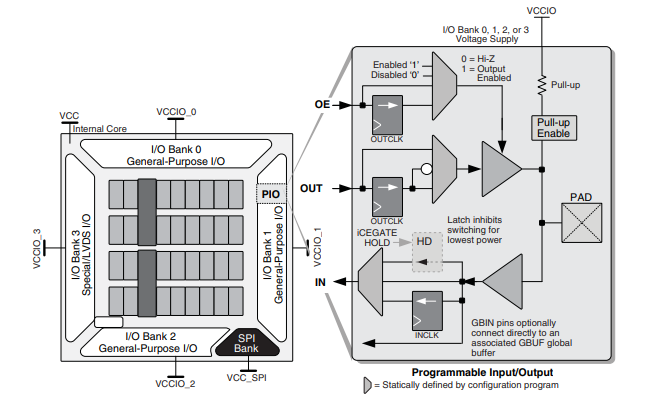

PIO包含三个块:一个输入寄存器块,一个输出寄存器块iCEgateTM和一个三态寄存器块。为了节省电力,可选的iCEgateTM锁存器可以有选择地冻结IO组内单个、非注册输入的状态。

注意,冻结信号对银行来说是常见的。这些模块可以在各种模式下操作,以及必要的时钟和选择逻辑。输入寄存器组所有edqes上的pio的输入寄存器块包含寄存器,可以用来在高速接口信号被传递到设备核心之前对其进行条件调整。在一般的DDR模式中,两个寄存器被用来采样系统时钟信号的正边缘和负边缘上的数据,创建两个数据流。输出寄存器组输出寄存器块可以选择性地在信号被传递到syslO缓冲区之前对来自设备核心的信号进行寄存器。在一般的DDR模式中,两个寄存器被用来捕获系统时钟的正负边缘上的数据,然后混合创建一个数据流。

通电时典型的VO行为Vcc时,内部通电复位(POR)信号失效。Vcco 2, Vpp 2v5, Vcc SPI已经达到本数据表直流和开关特性部分的上电复位电压表中定义的水平。POR信号去激活后,FPGA核心逻辑激活。用户有责任确保所有的Vcco库都是活跃的,具有有效的输入逻辑级别,以适当地控制对应用程序至关重要的所有I/O库的输出逻辑状态。设备I/O引脚的默认配置在配置之前是通过Vcco的弱上拉来进行三次陈述的。I/O引脚将保持预配置状态,直到Vcc和Vccio(用于包含配置VOs的I/O银行)达到水平。此时,VOs将只在正确的下载/配置后才进行软件用户配置设置。

未使用的IOs会被自动阻塞,并禁用拉出终止支持标准iCE40 syslO缓冲器支持单端和差分输入标准。支持的单端标准是LVCMOS。缓冲区支持LVCMOS 1.8, 2.5, 3.3V标准。缓冲区有单独配置的总线维护选项(弱拉起或无)表2-7和表2-8列出了iCE40设备支持的VO标准(包括供电电压和参考电压)。

| 型号 | 品牌 |

| iCE40LP1K-CM81 | Lattice |

| iCE40LP1K-QN84 | Lattice |

| ICE40LP1K-SWG16TR1K | Lattice |

| ICE40LP1K-SWG16TR50 | Lattice |

| ICE40LP384-CM36 | Lattice |

| ICE40LP384-CM49 | Lattice |

| ICE40LP384-SG32 | Lattice |

| ICE40LP384-SG32TR | Lattice |

| iCE40LP4K-CM121 | Lattice |

| iCE40LP4K-CM225 | Lattice |

| iCE40LP4K-CM81 | Lattice |

| iCE40LP4K-CM81TR | Lattice |

| ICE40LP640-SWG16TR1K | Lattice |

| iCE40LP8K-CM121 | Lattice |

| iCE40LP8K-CM225 | Lattice |

| iCE40LP8K-CM81 | Lattice |

| ICE40UL1K-CM36AI | Lattice |

| ICE40UL1K-CM36AITR | Lattice |

| ICE40UL1K-CM36AITR1K | Lattice |

| ICE40UL1K-SWG16ITR | Lattice |

| ICE40UL1K-SWG16ITR1K | Lattice |

| ICE40UL1K-SWG16ITR50 | Lattice |

| ICE40UL640-CM36AI | Lattice |

| ICE40UL640-CM36AITR | Lattice |

| ICE40UL640-CM36AITR1K | Lattice |

| ICE40UL640-SWG16ITR | Lattice |

| ICE40UL640-SWG16ITR1K | Lattice |

| ICE40UL640-SWG16ITR50 | Lattice |