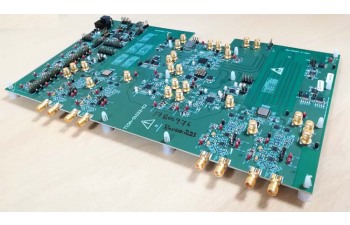

这种高速多通道数据采集参考设计可实现最佳系统性能。系统设计人员需要考虑关键设计参数,例如高速多通道时钟生成的时钟抖动和偏斜,这会影响整体系统 SNR、SFDR、通道间偏斜和确定性延迟。此参考设计展示了多通道 AFE 和时钟解决方案,该解决方案使用带 JESD204B 的高速数据转换器、高速放大器、高性能时钟和低噪声电源解决方案,以实现最佳系统性能

用于高性能接收器的 3.2 Gsps、1.5 GHz 多通道高速模拟前端

< 5 ps 通道间时钟偏差

多通道 JESD204B 投诉时钟解决方案

用于引脚兼容的 ADC12DJxx00 系列的可扩展平台

支持 TI 的高速转换器和采集卡 (TSW14J56 / TSW14J57)